Contoh Laporan Akhir

11:30:00 AM

|

2. Alat dan bahan[Kembali]

a.. Jumper

Gambar 1. Jumper

b.Panel DL 2203D

c.Panel DL 2203C

d.Panel DL 2203S

Gambar 2. Modul De Lorenzo

2.2 Bahan (proteus) [kembali]

a. IC 7408 (JK filp flop)

Gambar 3. IC 74LS112

b. IC 7404

c. IC 7432

b. Power DC

3. Rangkaian Simulasi[Kembali]

4. Prinsip Kerja[Kembali]

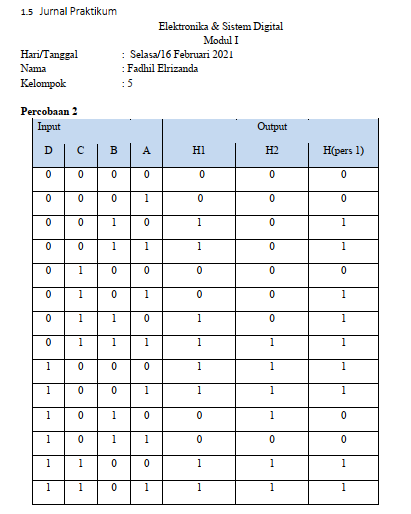

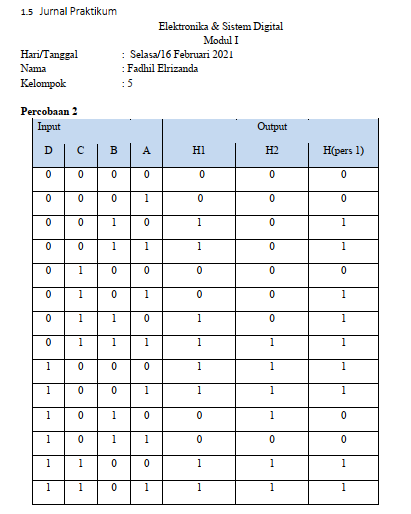

Rangkaian pada percobaan 2 terdiri atas 2 buah rangkaian yang menggunakan 1 buah gerbang XOR, 1 buah gerbang AND 3 input, 1 buah gerbang OR 2 input, logic state, dan logic probe. logic state yang terdapat pada rangkaian ini digunakan untuk mengatur input awal. Lalu logic state ini terhubung ke masing-masing input dari gerbang XOR dan AND. Untuk input dari gerbang XOR diberi nama yaitu input B dan D, input dari gerbang AND adalah A, C’, dan D. Kemudian untuk gerbang OR, inputnya adalah berupa output dari gerbang XOR dan AND. Kemudian output akhir dari gerbang OR ditunjukkan dengan logic probe yang akan berlogika 1 atau berlogika 0. Percobaan ini dapat membentuk beberapa kondisi sesuai dengan inputan awalnya.

Percobaan ini menggunakan prinsip gerbang logika. Gerbang XOR outputnya akan berlogika 1 ketika salah satu inputnya berlogika 1 (kedua input berbeda), yaitu 0 1 atau 1 0, dan akan berlogika 0 ketika kedua inputnya sama yaitu 0 0 atau 1 1. Gerbang AND outputnya akan berlogika 1 hanya ketika semua inputnya berlogika 1. Kemudian gerbang OR outputnya akan berlogika 1 ketika ada inputnya yang berlogika 1, dan akan berlogika 0 ketika semua inputnya berlogika 0.

Untuk rangkaian pertama, ketika kondisi inputan awal A, B, C, D, secara berturut-turut adalah semuanya 0, maka output yang dihasilkan adalah 0, yaitu kondisi logic probe 0. Ini terjadi karena ketika kedua input pada gerbang XOR (input B dan D) berlogika 0, maka output pada gerbang XOR adalah 0. Kemudian input gerbang AND (input A dan D) adalah 0, dan input C' adalah 1, maka outputnya juga 0. Sehingga input gerbang OR keduanya adalah 0, maka output akhirnya juga adalah 0, kondisi logic probe 0. Untuk rangkaian kedua, ketika kondisi inputan awal A, B, C, D, secara berturut-turut adalah semuanya 0, maka output yang dihasilkan adalah 0, yaitu kondisi logic probe 0. Ini terjadi karena ketika kedua input pada gerbang XOR (input B dan D) berlogika 0, maka output pada gerbang XOR adalah 0. Kemudian input gerbang AND (input A dan C) adalah 0, dan input B' adalah 1, maka outputnya juga 0. Sehingga input gerbang OR keduanya adalah 0, maka output akhirnya juga adalah 0, kondisi logic probe 0.

Untuk rangkaian pertama, ketika kondisi inputan awal A, B, C, D, secara berturut-turut adalah semuanya 1, maka output yang dihasilkan adalah 0, yaitu kondisi LED mati. Ini terjadi karena ketika kedua input pada gerbang XOR (input B dan D) berlogika 1, maka output pada gerbang XOR adalah 0. Kemudian input gerbang AND (input A dan D) adalah 1, dan input C' adalah 0, maka outputnya adalah 0. Sehingga input gerbang OR adalah 0 dan 0, maka output akhirnya adalah 0, kondisi logic probe 0. Untuk rangkaian kedua, ketika kondisi inputan awal A, B, C, D, secara berturut-turut adalah semuanya 1, maka output yang dihasilkan adalah 0, yaitu kondisi logic probe 0. Ini terjadi karena ketika kedua input pada gerbang XOR (input B dan D) berlogika 1, maka output pada gerbang XOR adalah 0. Kemudian input gerbang AND (input A dan C) adalah 1, dan input B' adalah 0, maka outputnya adalah 0. Sehingga input gerbang OR adalah 0 dan 0, maka output akhirnya adalah 0, kondisi logic probe 0. Percobaan ini dapat membentuk beberapa kondisi sesuai dengan inputan awalnya sesuai yang terdapat pada jurnal.

5. Video Praktikum[Kembali]

Percobaan 1:

1. Bandingkan rangkaian 1 (Output H1) dan rangkaian 2 (Output H2)

Berdasarkan rangkaian 1 dan rangkaian 2. Maka dapat dilihat bahwa output dari

kedua rangkaian tersebut tidak sama meskipun memiliki gerbang yang sama

2. Jelaskan penyederhanaan persamaan aljabar boolean di modul sehingga di dapat

persamaan H1 dan H2 menggunakan hukum hukum aljabar boolean.

Pada kedua rangkaian H1 dan H2 terdapat gerbang yang sama. Pada rangkaian H1

didapatkan AC’D + B(+)D

Dimana terdapat inverter pada C, gerbang AND pada A,C dan D,Gerbang XOR pada

B dan D serta gerbang OR padahasil output AC’D dan B(+)D

Pada rangkaian H2 didapatkan ABC’ + B(+)D

Dimana terdapat inverter pada C, gerbang AND pada A,B dan C,Gerbang XOR pada

B dan D serta gerbang OR padahasil output ABC’ dan B(+)D

3. Jelaskan mengenai peta karnough beserta POS dan SOP

Peta Karnaugh atau Karnaugh Map atau K-Map adalah suatu teknik penyederhanaan

ekspresi aljabar Boole (fungsi logika aljabar Boolean) dengan cara pemetaan

SOP

Perpaduan nilai-nilai peubah yang menghasilkan nilai fungsi sama dengan 1 adalah

001, 100, dan 111, maka fungsi Booleannya dalam bentuk kanonik SOP:

f(x, y, z) = x’y’z + xy’z’ + xyz

atau bisa (dengan menggunakan lambang minterm),

f(x, y, z) = m1 + m4 + m7 = (1, 4, 7)

POS

Kombinasi nilai-nilai peubah yang menghasilkan nilai fungsi sama dengan 0 adalah

000, 010, 011, 101, dan 110, maka fungsi Booleannya dalam bentuk kanonik POS

adalah

f(x, y, z) = (x + y + z)(x + y’+ z)(x + y’+ z’)

(x’+ y + z’)(x’+ y’+ z)

atau dalam bentuk lain,

f(x, y, z) = M0 M2 M3 M5 M6 = (0, 2, 3, 5, 6)

4. Selesaikan persamaan ajabar boolean pada modul menggunakan Peta karnough SOP

Dalam bentuk SOP maka yang dilihat adalah Y= 1. Dimana Y = H(pers1)